组合逻辑38译码器实现与相关语法基础

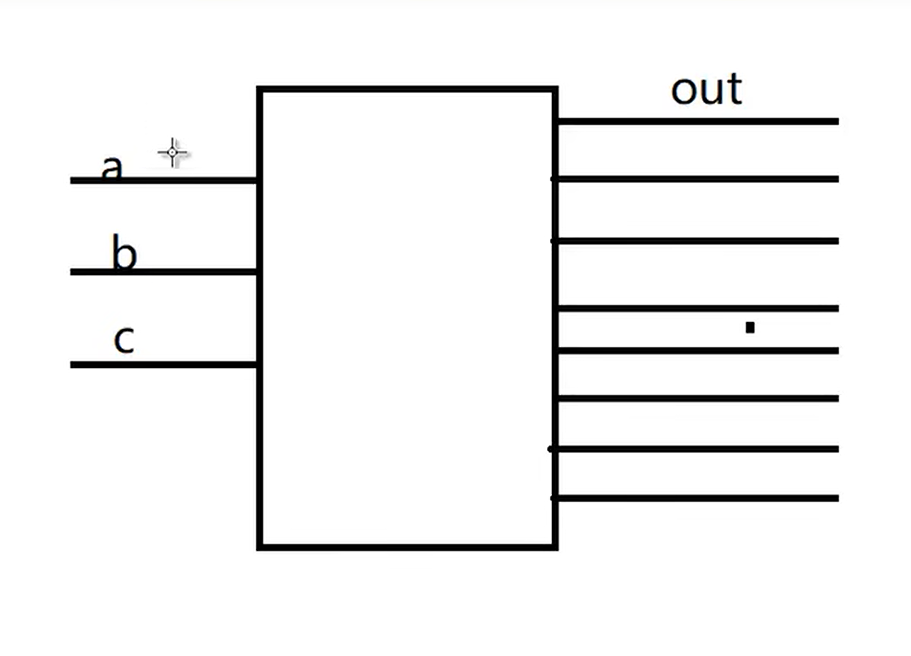

3-8译码器的结构

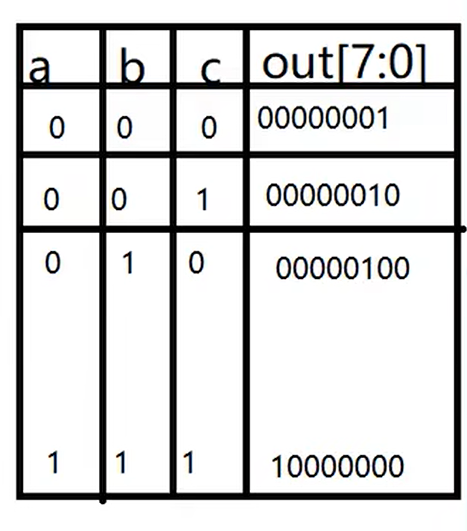

真值表如下:

显然就是用三个二进制表示8个要选择的电平。

译码器的代码编写

我们译码器的的代码和解释如下:

1 | module decoder_3_8(a, b, c, out); |

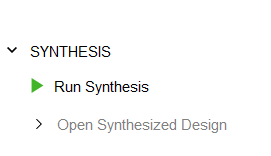

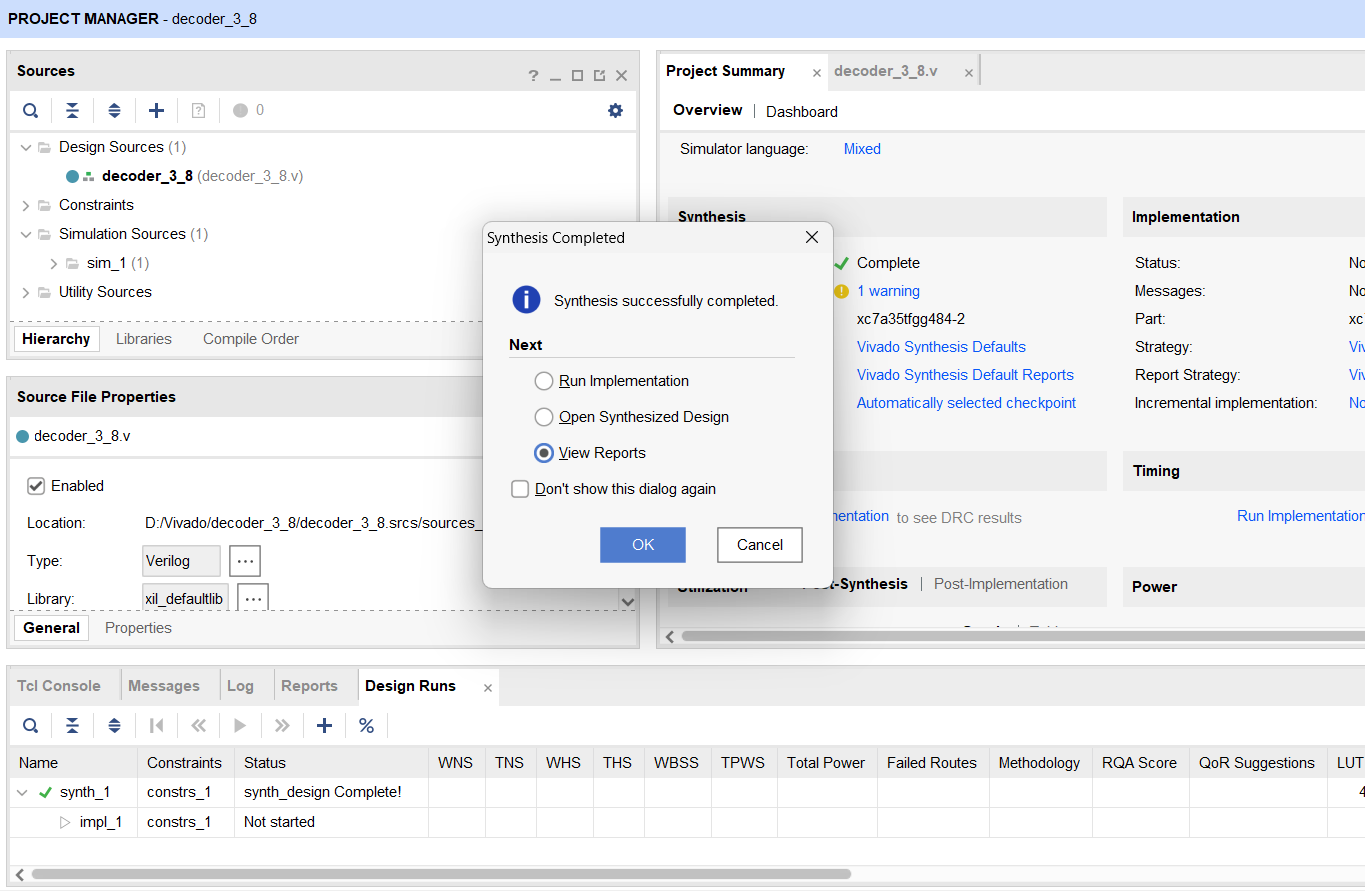

synthesis语法测试

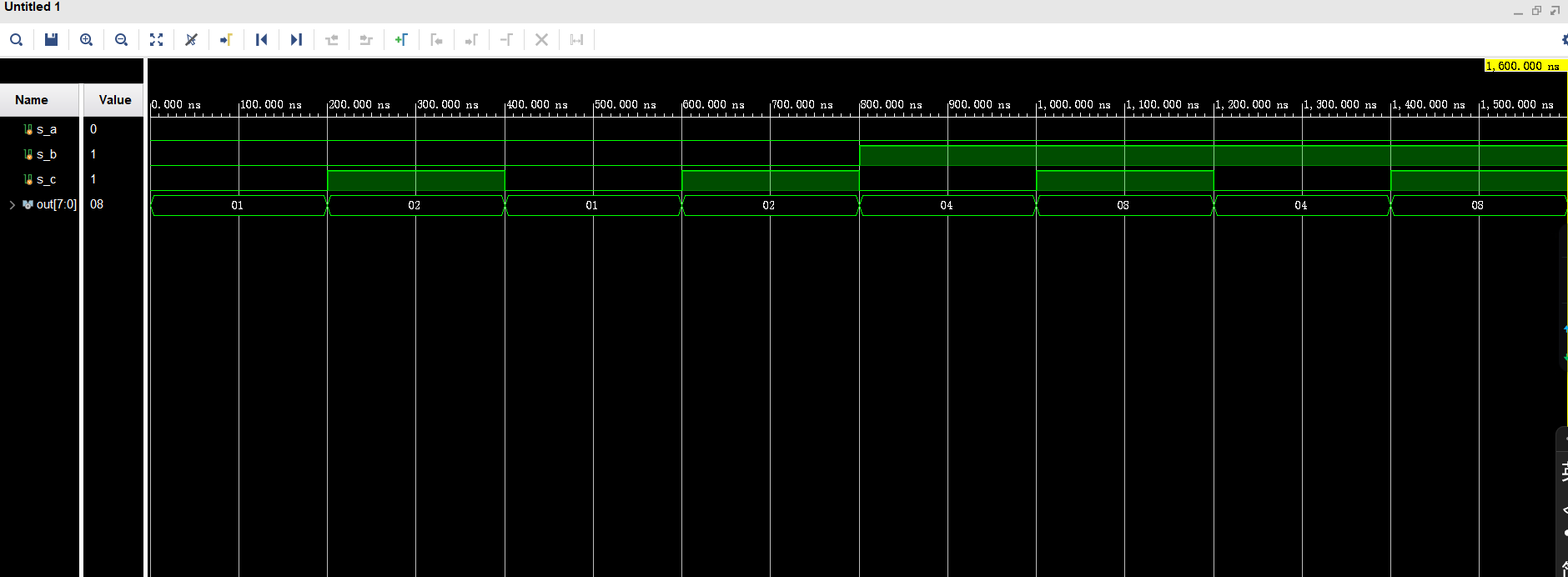

然后我们在左侧点击运行测试。

这是用来检查语法是否有错误的。出现弹框会让我们选cpu的个数,默认即可!等待一段时间,即可跑完,之后我们可以点击查看报告来确认是否正确。

然后还可以从message里面查看是否有语法错误。

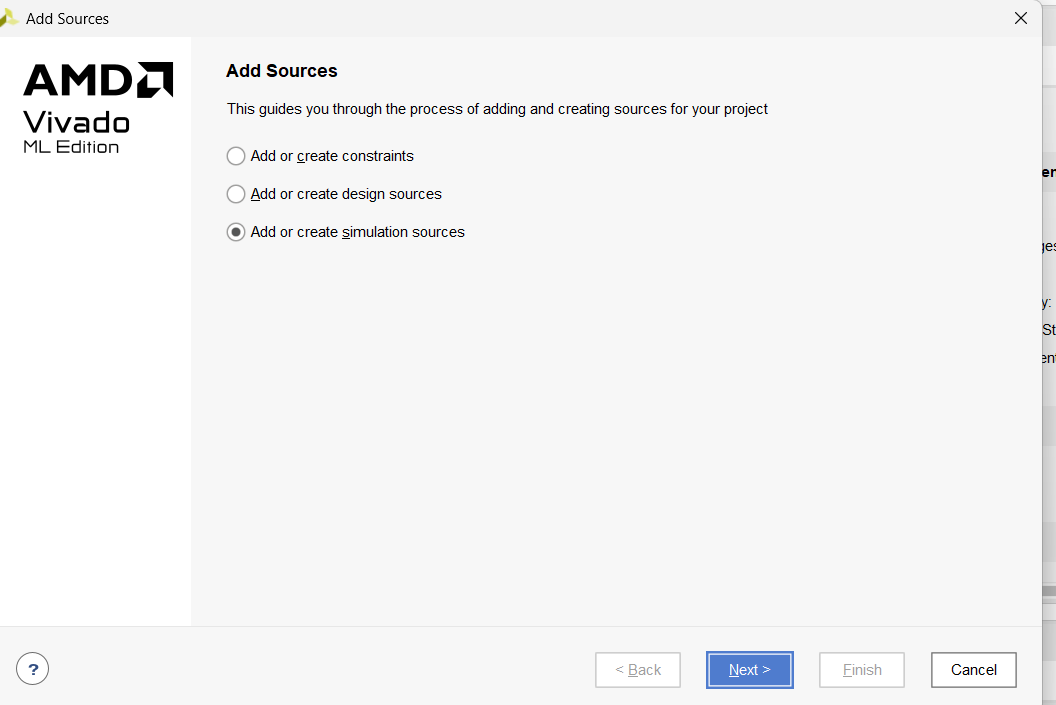

仿真测试

仿真测试我们在数字电路中学习过,其实就是加入一个示波器,并且给定不同状态的输入信号,output连接示波器,在输入变化期间,观察示波器的显示,确认电路逻辑无误。

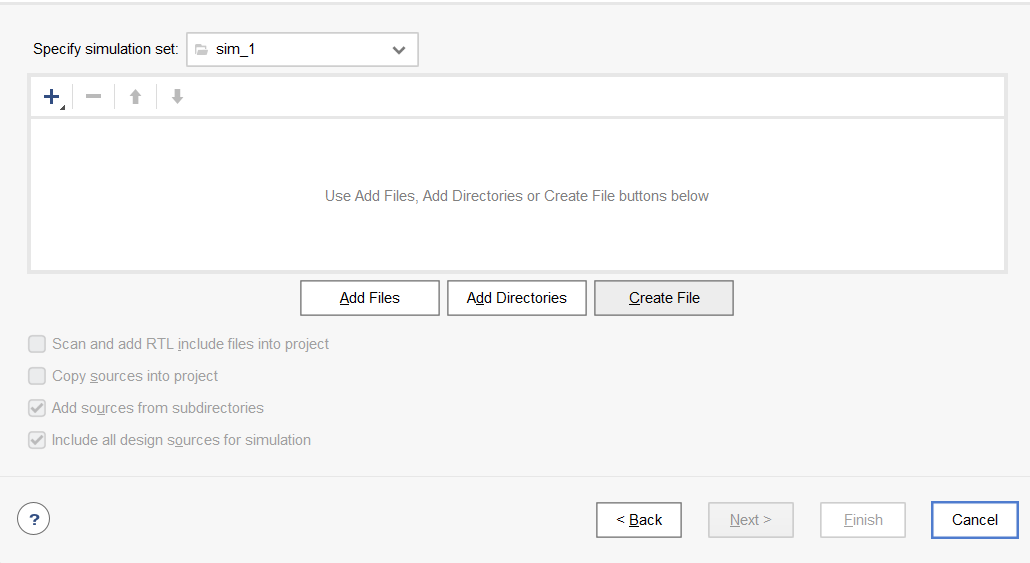

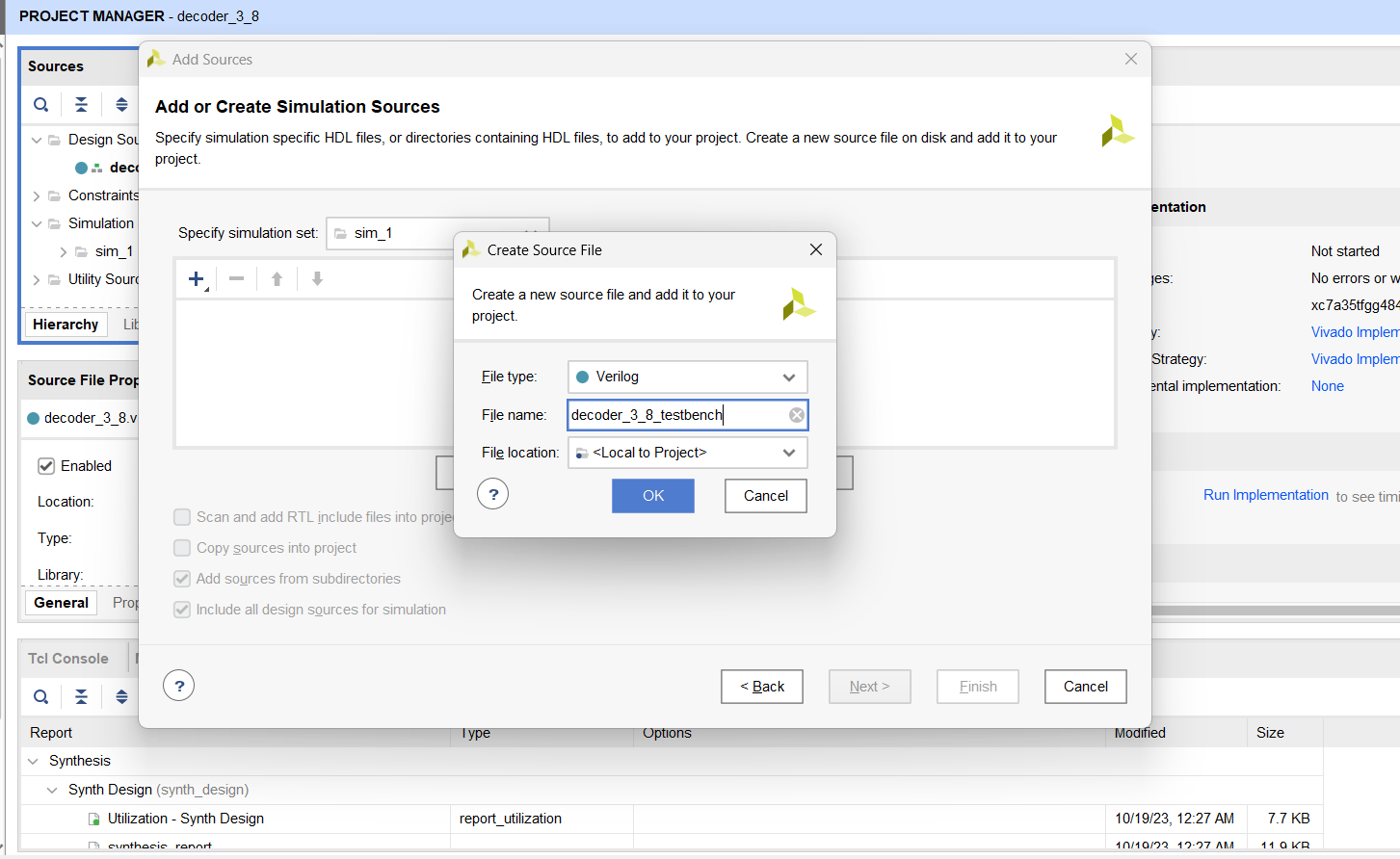

先点击添加源文件,创建一个仿真源文件

然后点击create_file创建文件。

然后输入我们给仿真文件的名字,就可以和我们工程的名字相同,这里统一用decoder_3_8来命名。

当然我在后面加上了testbench因为testbench是仿真文件的标识符。然后完成创建,开始编辑testbench文件。

代码如下:

1 |

|

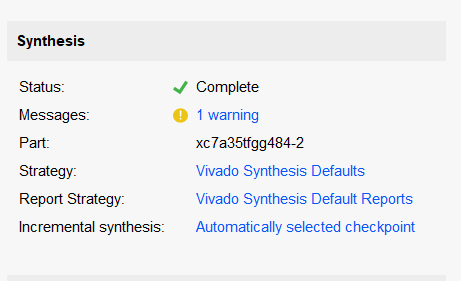

我们可以先再运行一下synthesis来检查一下语法问题,当然这里我就跳过了,不建议大家都跳过,如果是刚开始学没多久的话。

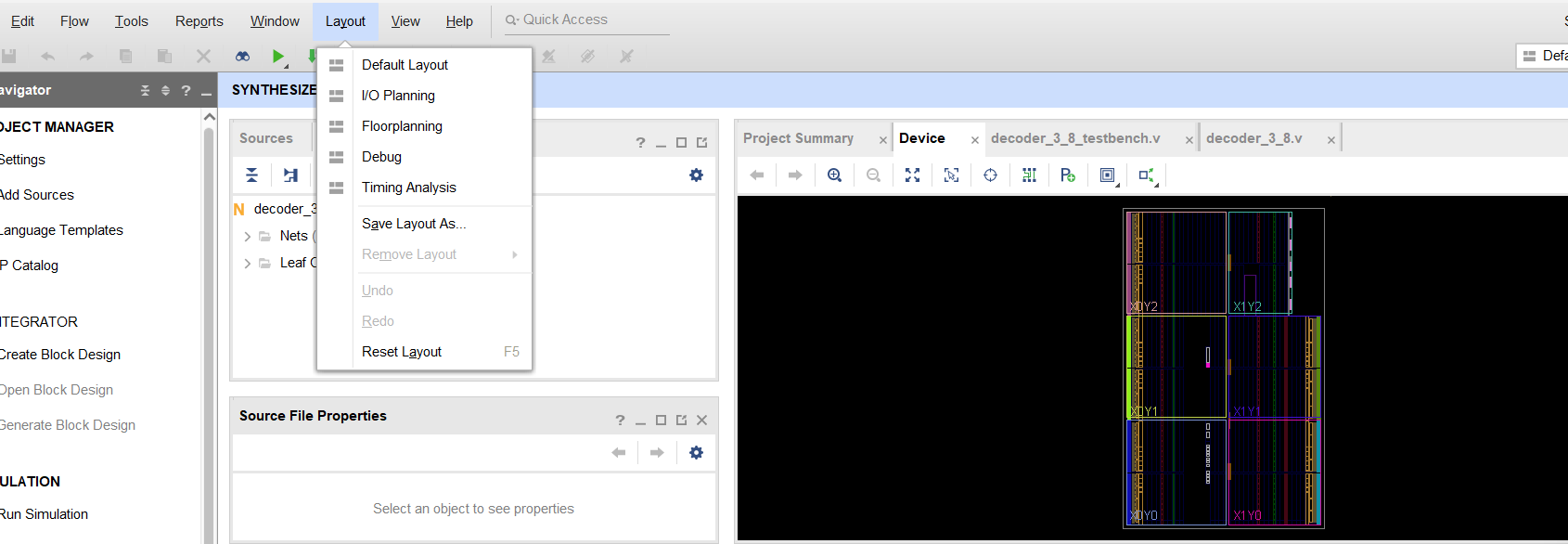

点击上面栏里的求和

符号可以查看simulation和synthesis状态。

可以看到没有错误,然后运行仿真。

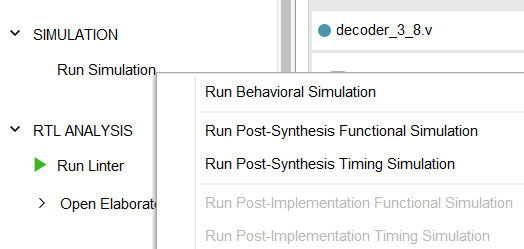

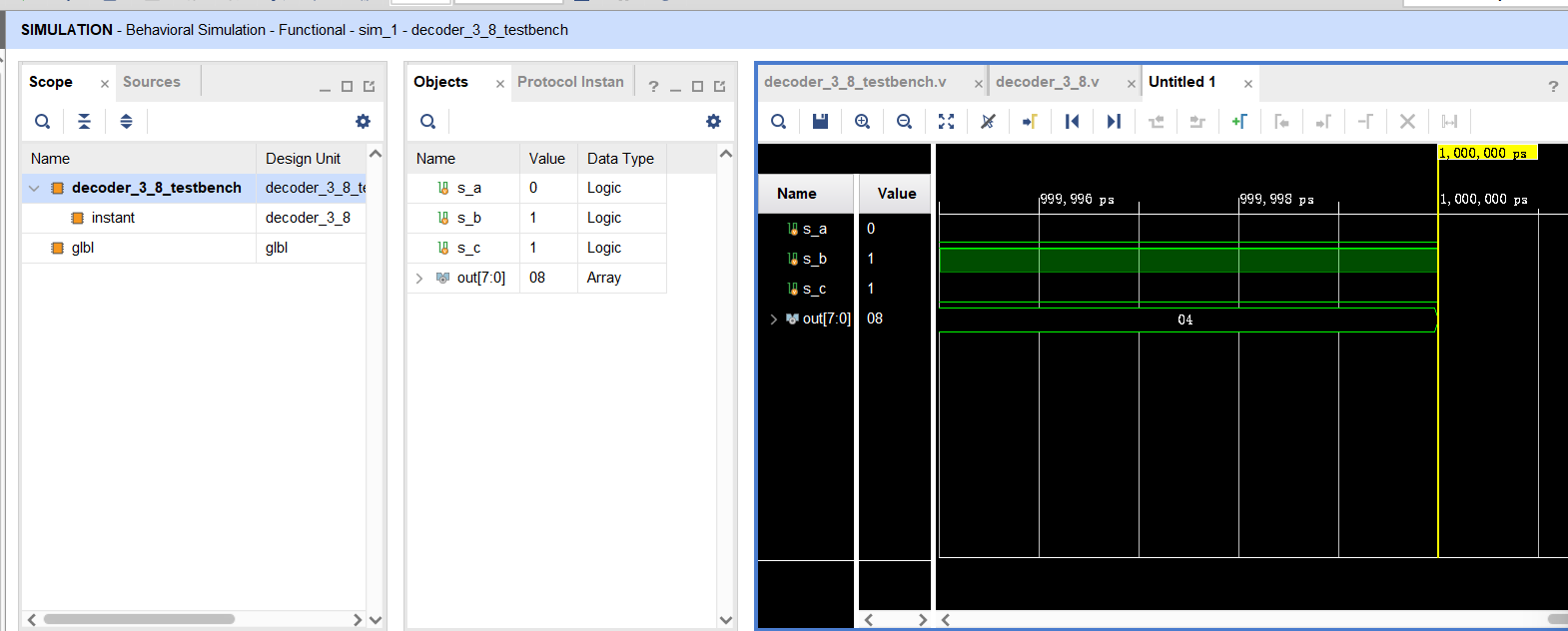

我们先运行behavior仿真,也就是理想仿真情况,不存在门电路延迟现象。结果如图所示:

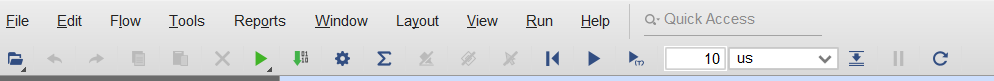

软件默认只能跑1000ns,但是我们程序总共要跑1600ns,所以可以让他跑完。

点击这里的播放键,就可以跑完了。

然后放大可以看到全图。我这里点击了图中栏上的四个箭头扩张键,就可以放大时间轴了。

引脚分配

然后我们开始硬件的引脚分配

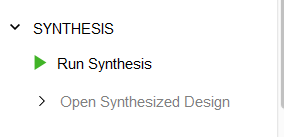

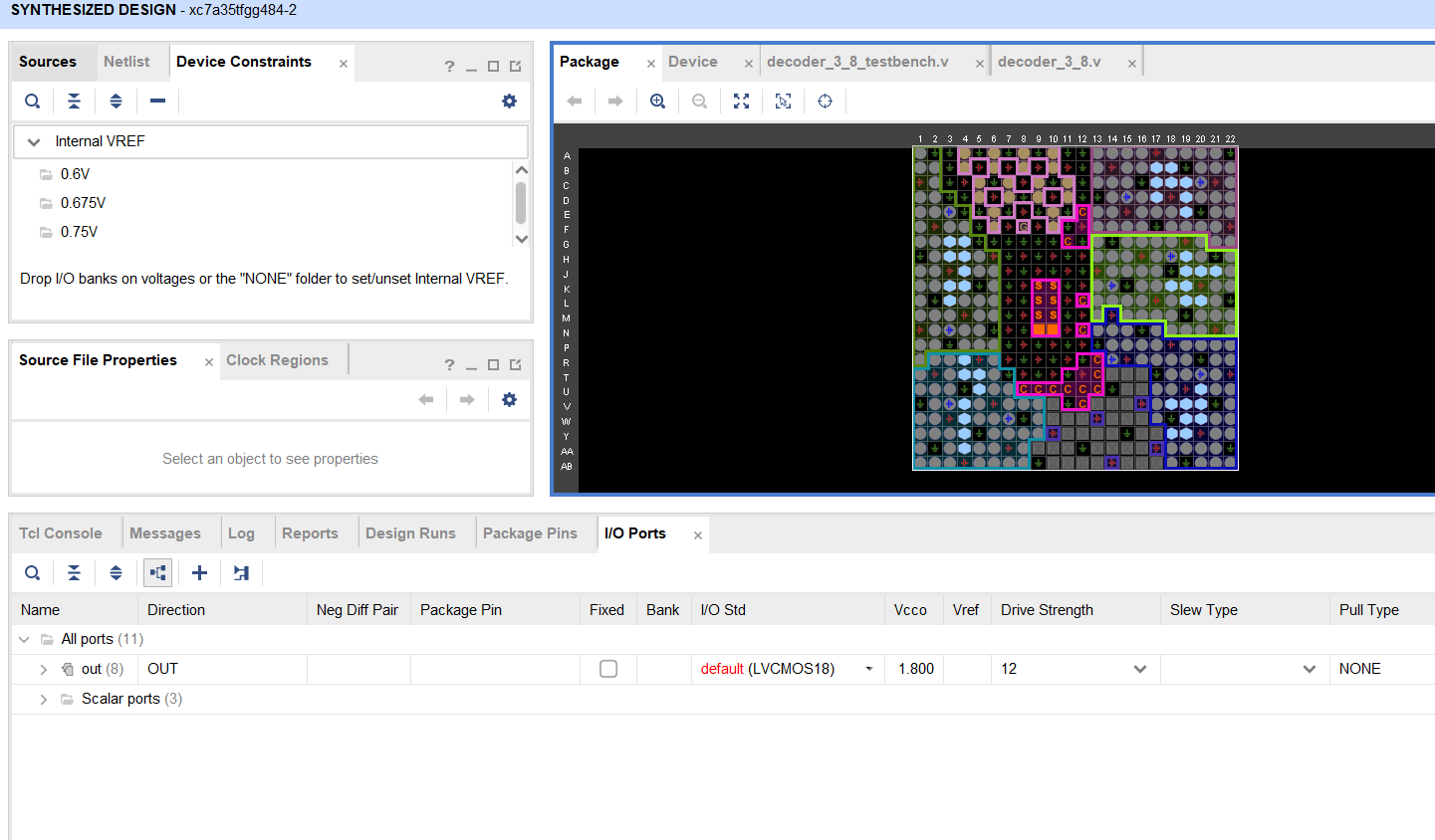

点击下面的open synthesized design

然后看到弹出的device画面,再点击layout中的io planning

便显示出了我们选的具体板子的io引脚图。

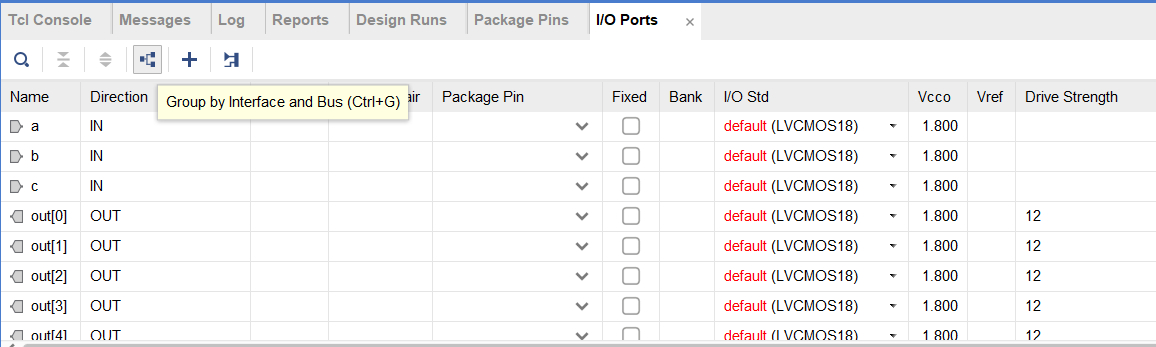

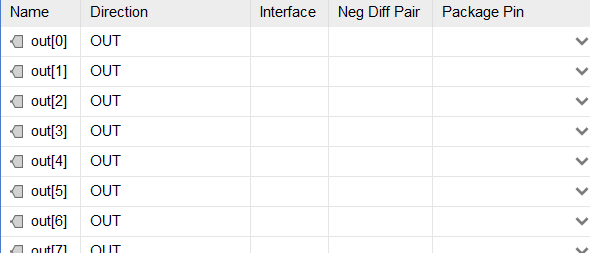

然后在下面我们点击这个,更方便的查看引脚对应我们的变量名。

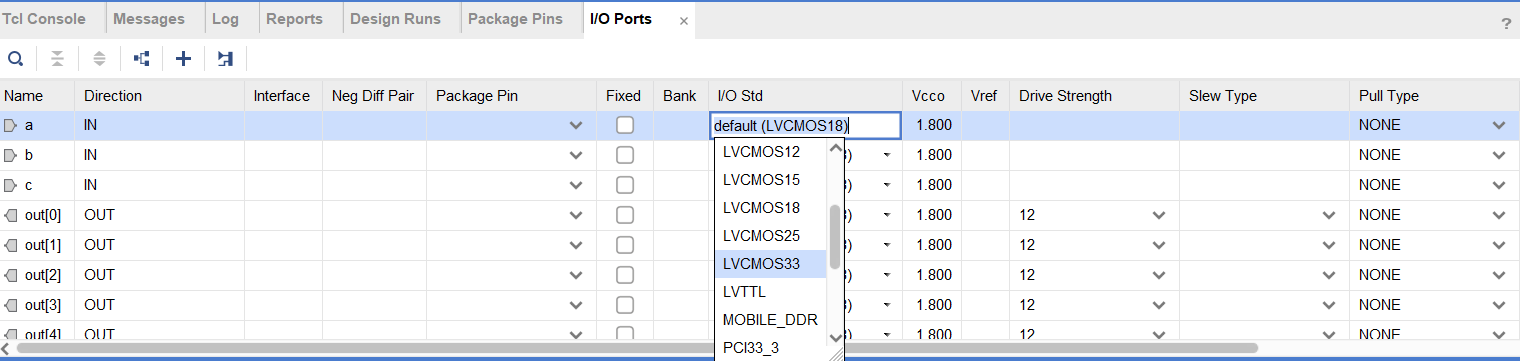

然后把所有的IO表准都改成如下格式。

都改成33结尾的。

在实际开发板上

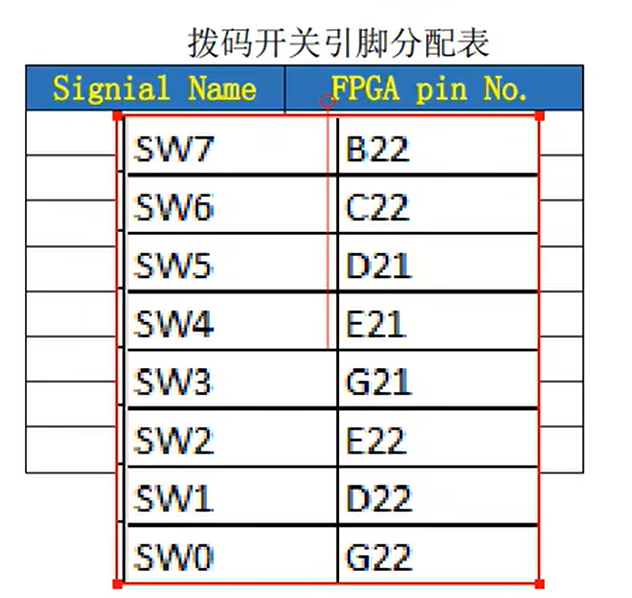

我们看到8个拨动开关,超过3个,可以用来选三个作为输入。

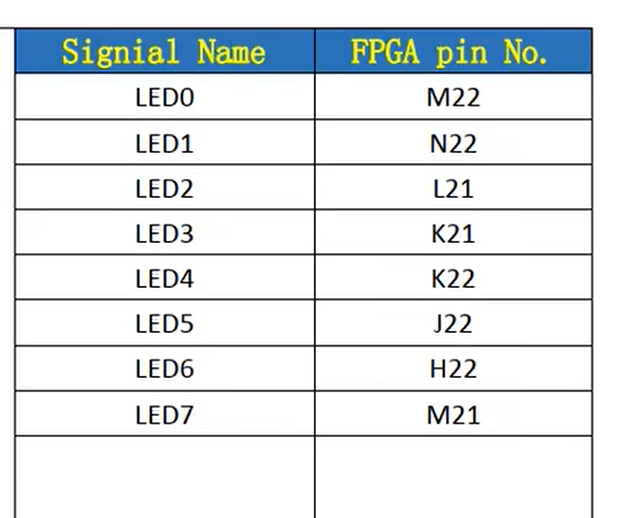

我们看一下引脚说明书。

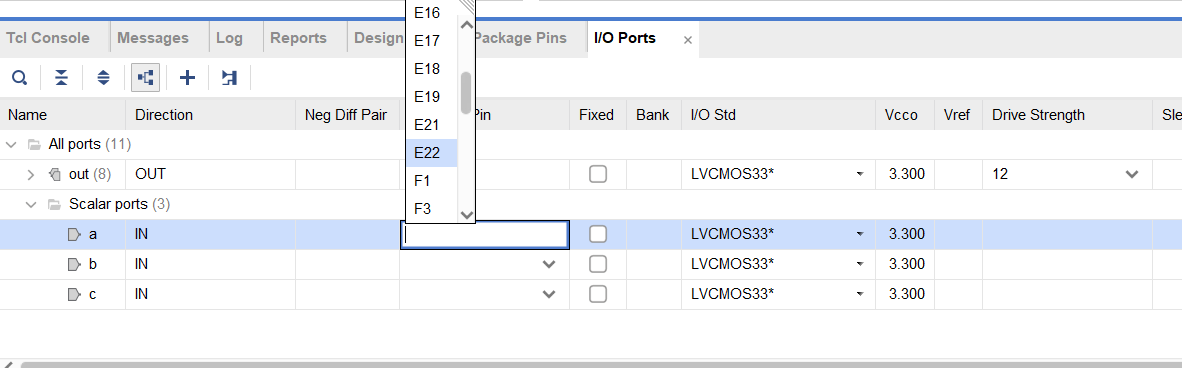

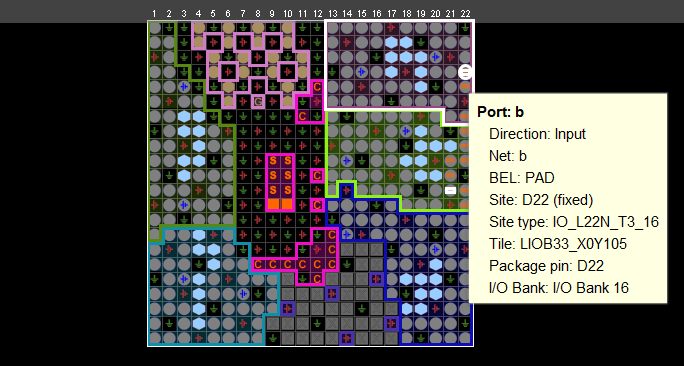

这是这8个拨动开关的名字和编号。比如我们把输入a给SW2,那么对应就要选择E22。

比如我们把b给SW1,那么就要选择D22。我不再截图。

out我们用LED灯来显示,找一个灯的接口赋值给output即可。观察输出即可看亮度。

对应此LED接口表连接即可。

我们直接让out[0]输出到灯LED0,以此类推。

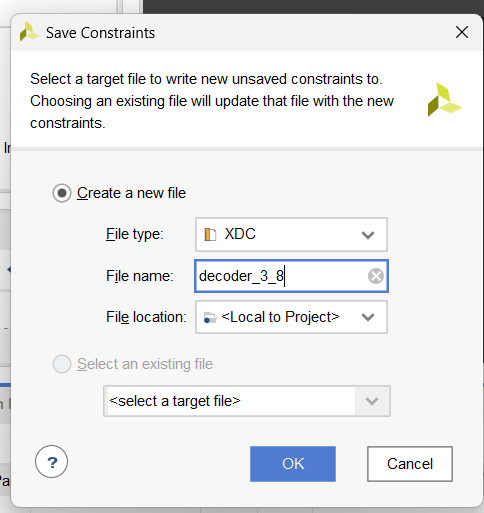

然后ctrl+s保存即可。遇见弹框直接点OK。然后输入文件名。

保存即可。

可以找到一些被我们分配的IO口。

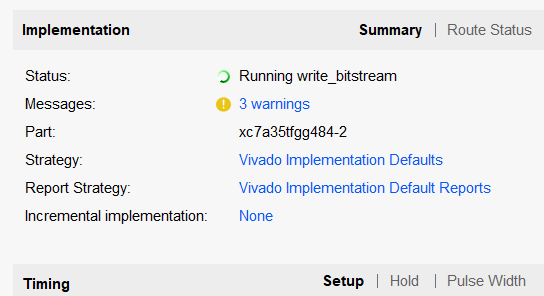

implementation or directly generate bitstream

也就是我们可以直接点击generate bitstream键一步到位。implementation用来布局布线,generate bitstream自动执行布局布线的操作。

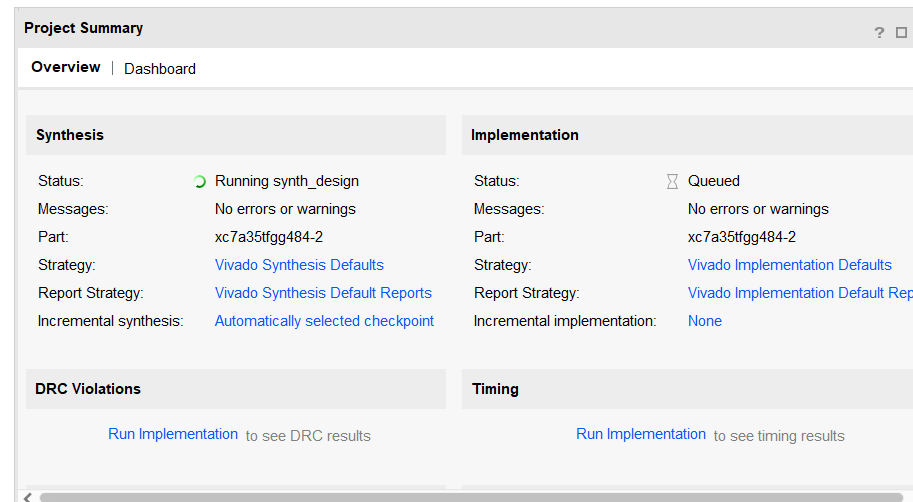

我重启了项目之后点击了implementation可以看到它会自动先从synthesis开始运行。

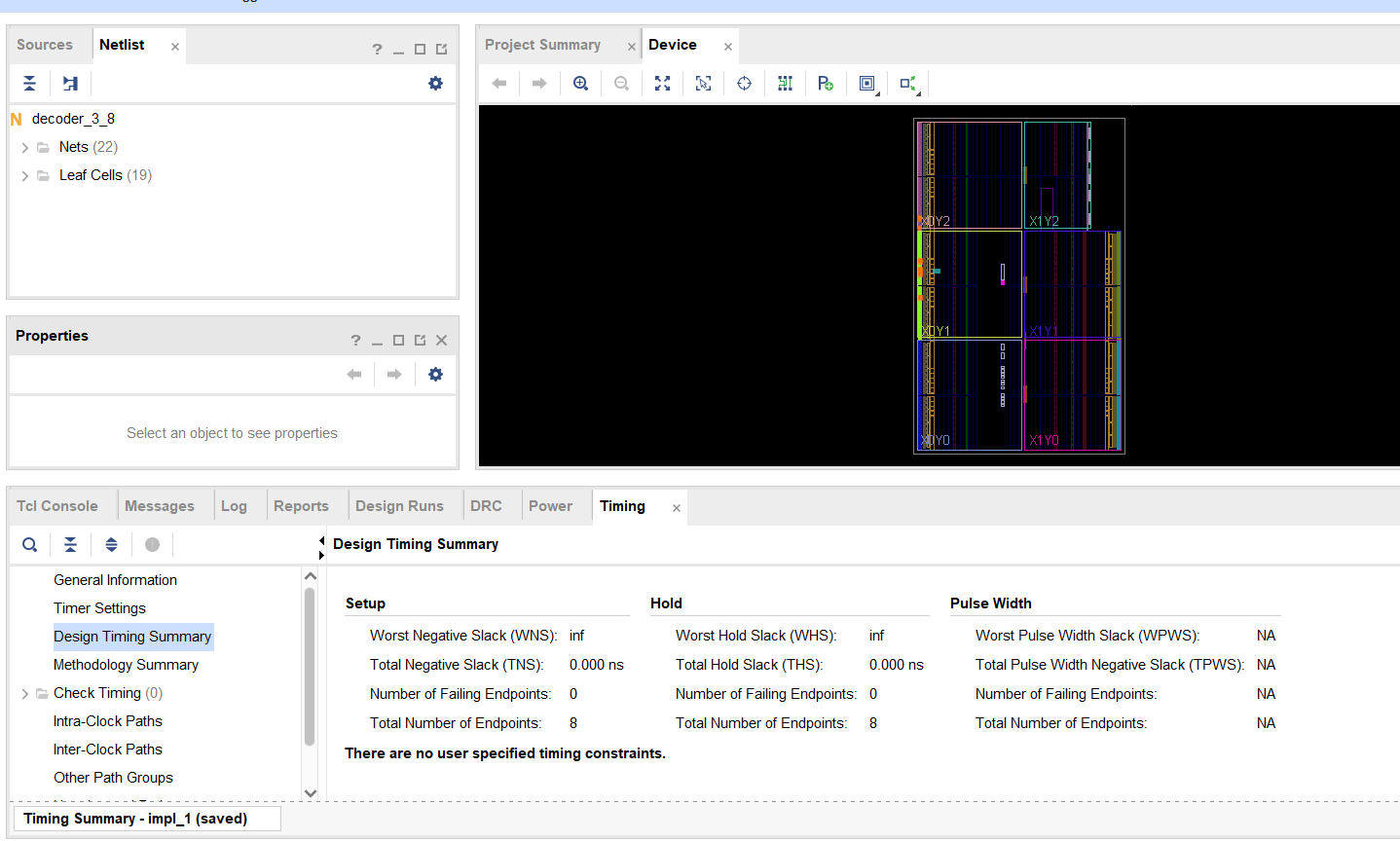

结束之后我们点击打开implemented design

如图所示,没有什么我们需要关注的。

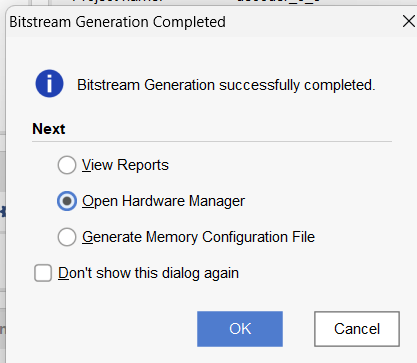

然后生成比特流即可!

这里会显示状态。

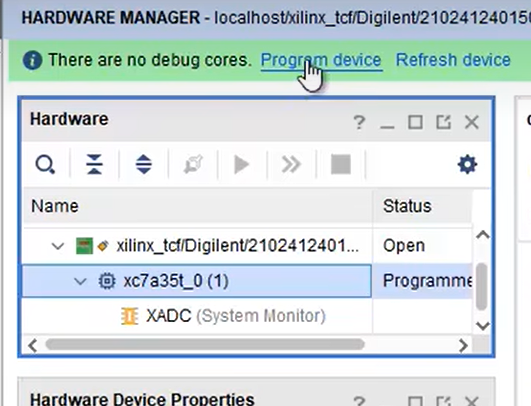

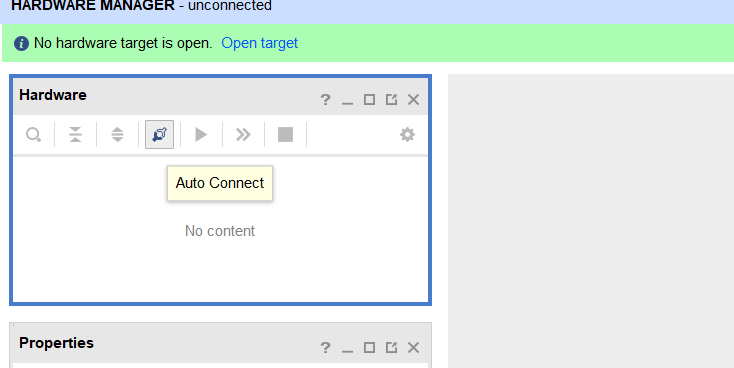

然后我们打开硬件管理器,准备连接到硬件并且将比特流下载到硬件。

插上硬件之后点击

即可。

最后点击program devive即可下载过去。然后直接在开发板对应输入开关处来回拨动即可。查看LED灯状态。